# A Novel Approach of Low Power Low Voltage Dynamic Comparator Design for Biomedical **Application**

<sup>1</sup>Nitesh Kumar, <sup>2</sup>Debasish Halder, <sup>3</sup>Mohan Kumar 1,2,3 M.Tech in VLSI Design <sup>1,2,3</sup>School of VLSI Design and Embedded Systems, <sup>1,2,3</sup>National Institute of Technology Kurukshetra, Haryana 136119, India

Abstract—A low power dynamic comparator capable of detecting a minimum input voltage difference of 100µV is presented in this article. The comparator is designed and simulated with a supply voltage of both 0.4 V and 1.2 V using UMC 180 nm CMOS technology. All the transistors are compelled to work in the sub-threshold region while working with the supply voltage of 0.4 V. But in case of 1.2 V supply voltage it works in normal region. It consumes 74.09nW power at a frequency of 2 MHz and 136.2 ns delay with a of 0.4 V supply voltage while in case of 1.2 V it consumes 155.70 µW power at a frequency of 500 MHz and 381ps delay. (Abstract)

Index Terms— Double-tail comparator, dynamic clocked comparator, ultra-low power, sub-threshold, biosensors, bioelectronics, implantable devices. (key words)

### I. Introduction

Since the invention of first integrated circuit by J. Kilby and R. Noyce in the late 1950s, microelectronics industry has shown an un-dominatable agility to find new dimensions of growth. From the starting of mid 90s it show a new direction of growth opportunity i.e. medical industry. Advancing in microelectronics is also given new possibilities to medical science. Wearable devices have shifted the health care from the hospital to home and allowed to live normal life.

A low power, low-offset, moderate speed comparator is a very important circuit block for biomedical implant devices [1]. There are different types of comparator which can provide the moderate to high speed, like latched comparator, multistage open loop comparator and the dynamic comparator. However the dynamic latch comparator is limited by a huge offset voltage which remarkably affects the resolution whereas bandwidth of amplifier limits the open loop comparator's efficiency. With low offset some architecture on dynamic comparators have already presented in some previous research work but with the cost of high power consumption [2-4]. In [5-7], some conventional dynamic comparators are designed which are capable of working at low voltage without degrading the performance of the circuit. In [7] a comparator is proposed which consumes 18µW while working at a frequency of 600 MHz with a low supply voltage of 0.5V. In [8] a comparator is proposed which works with a supply voltage of 0.6 V and consumes 153µW power while the clock frequency is 1.1GHz. The design architecture of a double-tail dynamic comparator is first proposed in [9] which has separated cross-coupled stage and input stage. As a result, this double-tail comparator can operate fast over a wide range of supply and common mode voltage. In this article, a detailed analysis of a proposed dynamic comparator is presented which is working in sub-threshold region and consumes a considerably low power.

## II. DYNAMIC COMPARATOR

Clocked regenerative comparators widely used in high-speed ADCs because of positive feedback in regenerative latch they can operate at faster speed. Many comprehensive analyses of different comparator architecture had already been presented, which investigated different performance of these comparators, like offset [10-12], noise [13], kick-back noise [14] and random decision errors [15]. In this section, an analysis on both the sub-threshold conventional and the sub-threshold dynamic double-tail comparator is done.

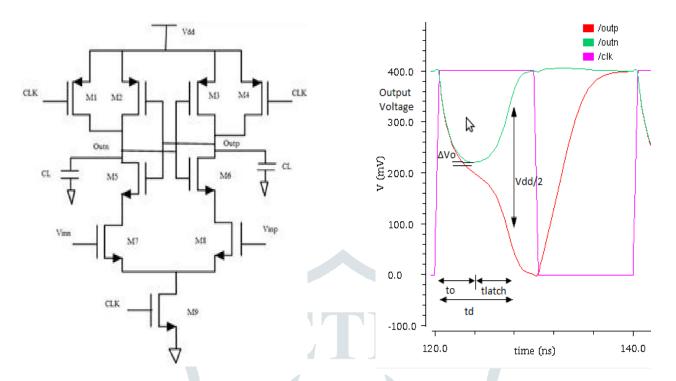

## CONVENTIONAL DYNAMIC COMPARATOR

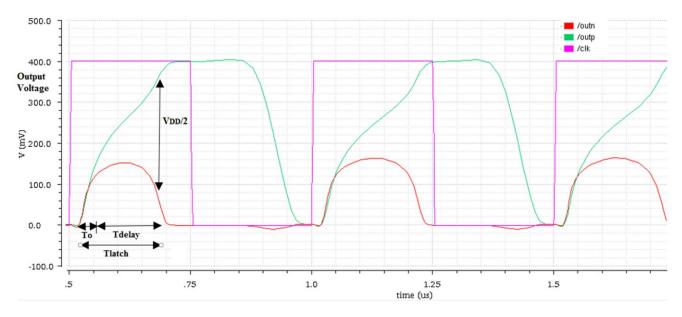

In figure 3.1 the circuit diagram of the sub-threshold conventional dynamic comparator [9] is shown. When Clock = Gnd the circuit is said to be in reset phase transistor  $M_9$  is off, transistors  $M_I$ - $M_4$  charge both the output nodes (Outn, Outp) to  $V_{DD}$  (high) which defines the circuit's start condition. When Clock =  $V_{DD}$  the circuit is said to be in evaluation phase  $M_I$  and  $M_4$  transistors are off, and  $M_9$  (the tail transistor) is on. Output voltages (Outp,Outn), which were charged to  $V_{DD}$  voltage in reset phase, will discharge but the discharging rates are different. Figure 3.2, shows the total delay of this comparator which has two time delays,  $t_0$ and  $t_{latch}$ . The delay  $t_0$  represents the time taken by load capacitance  $C_L$  to discharge until the  $M_2$  or  $M_3$  transistor turns on. Let the case be, where the input voltage at node  $V_{inp}$  is higher than  $V_{inn}$  (i.e.,  $V_{inp} > V_{inn}$ ), the drain current ( $I_8$ ) of  $M_8$  transistor causes fast discharge of Outp node as compared to Outn node, which is driven by  $M_7$  transistor with smaller current.

Now, the discharge delay can be given by equation (1),

$$t_0 = \frac{c_L |V_{thp}|}{l_2} \cong 2 \frac{c_L |V_{thp}|}{t_{tail}} \qquad \dots (1)$$

Where I<sub>2</sub> is given by

Where

$$I_2$$

is given by

$$I_2 = \frac{I_{tail}}{2} + \Delta I_{in} = I_{tail/2} + g_{m7,8} \Delta I_{in} \qquad ... (2)$$

Where  $I_{tail}$  is the current of transistor  $M_9$ .

The latch delay can be given by equation (3),

$$t_{latch} = \frac{c_L}{g_{meff}} \cdot \ln\left(\frac{\Delta V_{out}}{\Delta V_0}\right) = \frac{c_L}{g_{meff}} \cdot \ln\left(\frac{V_{dd}/2}{\Delta V_0}\right) \qquad ... (3)$$

Where  $t_{latch}$ , is the latching of two cross-coupled inverters.

Where  $g_{meff}$  is the effective trans-conductance of the back to back inverters. The  $\Delta V_0$  is given by equation (4),

$$\Delta V_o = 2 \mid V_{thp} \mid \sqrt{\frac{\beta_{7,8}}{I_{tail}}} \Delta V_{in} \qquad \dots (4)$$

Where  $\beta_{7.8}$  is the current factor of input transistors.

The total delay  $t_{delay}$ [16] of the conventional dynamic comparator can be given by equation (5)

$$t_{delay} = t_o + t_{latch} = 2 \frac{c_l |V_{thp}|}{I_{tail}} + \frac{c_l}{g_{meff}} \cdot \ln \left( \frac{V_{DD}}{4 |V_{thp}| \Delta V_{in}} \sqrt{\frac{I_{tail}}{\beta_{7,8}}} \right) \qquad ...(5)$$

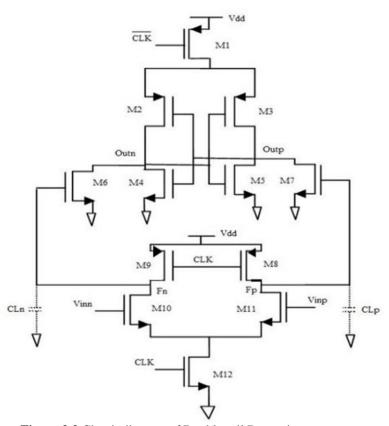

## DOUBLE TAIL DYNAMIC COMPARATOR

Figure 3.3 depicts the circuit diagram of double tail dynamic comparator operating in sub-threshold region. When clock = Gnd (low) the circuit is said to be in reset phase and the tail transistor  $M_1$  and  $M_{12}$  are off,  $M_8$  and  $M_9$  transistor charges nodes  $F_n$  and  $F_p$ to  $V_{DD}$ , which causes the transistor  $M_6$  and  $M_7$  to discharges the Output nodes(Outn, Outp) to ground. When clock =  $V_{DD}$ , the circuit is said to be in evaluation phase and the tail transistor  $M_1$ ,  $M_{12}$  are turned on and the Outp and Outn will start to charge. Transistor  $M_8$  and  $M_9$  are turned off and the voltage at nodes  $F_n$  and  $F_p$  will starts to drop. The discharge rate of  $F_n$  and  $F_p$  are different because it depends on the input voltages. Let the case be where  $V_{inn} > V_{inp}$ , in this case the discharge rate of node  $F_n$  will be more then node  $F_p$  and therefore transistor  $M_6$  and  $M_7$  will turn off at different time intervals. Thus Outn node will get charged to  $V_{DD}$ - $|V_{thp}|$  before the Outp node, the corresponding transistor  $M_3$  will be turned on and Outn discharges to ground and Outp will charge to V<sub>DD</sub> as shown in figure 3.4. The circuit works vice versa if Vinp>Vinn. The intermediate stage consists of transistors  $M_6$  and  $M_7$  passes the  $\Delta V_{Fn(p)}$  (input dependent differential voltage) voltage to cross coupled inverters and provide a batter shielding between input and Output, which results less kickback noise. The delay of conventional double-tail comparator consists of two parts,  $t_o$  and  $t_{latch}$ . The  $t_o$  delay characterizes the load capacitance  $C_{out}$  charging (at the output nodes, Outn and Outp) until the turns on of the first n-channel transistor  $(M_4/M_5)$ , after that the latch regeneration begins, thus  $t_o$  can be obtained

$$t_0 = 2 \frac{c_L v_{thp}}{I_{tail}}$$

... (6)

Where  $I_{BI} =$  drain current of the  $M_4 \approx$  half of tail current  $I_{tail2}$  ( $M_I$ ). The latch delay for the double tail comparator can be

$$t_{latch} = \frac{c_l}{g_{meff}} \cdot \ln\left(\frac{v_{DD/2}}{\Delta v_o}\right)$$

Output voltage difference at the time  $t_0$ ,  $\Delta V_o$  is given by

$$\Delta V_o = \left(\frac{2V_{thn}}{I_{tail2}}\right)^2 \cdot \frac{C_{L,out}}{C_{Ln(p)}} \cdot g_{mR10} \cdot g_{m10,11} \Delta V_{in} \qquad ... (8)$$

Substituting the

$$\Delta V_o$$

in  $t_{latch}$  the delay  $t_{delay}$  [16] of the conventional double tail comparator can be given by,

$$t_{delay} = t_o + t_{latch} = \frac{2V_{thn}C_{Lout}}{I_{tail2}} + \frac{C_{Lout}}{g_{meff}} \cdot \ln\left(\frac{V_{DD}.I_{tail}^2C_{Ln(p)}}{8V_{thn}^2.C_{Lout}.g_{mR10,11}\Delta V_{in}}\right) \dots (9)$$

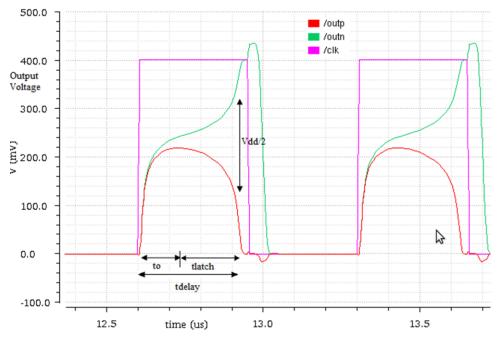

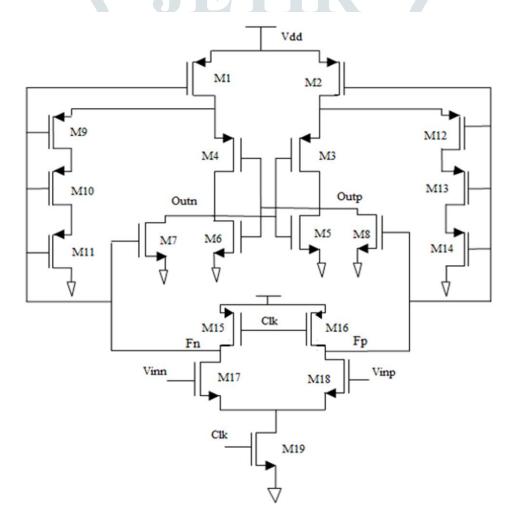

## PROPOSED DYNAMIC COMPARATOR

Figure 3.5 depicts the circuit diagram of proposed dynamic comparator which can be made to operate both in sub-threshold and normal saturation region. During reset phase Clock= Gnd (Low) and  $M_{19}$  tail transistor is off, transistor  $M_{15}$  and  $M_{16}$  charges nodes Fn and Fp to  $V_{DD}$  voltage, which causes the transistors  $M_7$  and  $M_8$  to discharge the output node to ground. In the decisive phase Clock =  $V_{DD}$  (High),  $M_{I9}$  tail transistor is turned on and  $M_7$ - $M_8$  turned off and the voltage at nodes Fn and Fp starts to drop. The transistor  $M_I$  and  $M_2$  and  $M_9$  to  $M_{I4}$  will be turned on when the voltage at the nodes Fn and Fp is low enough. Now the Outp and Outn can start to charge. Consider the case where Vinp > Vinn, in this case the discharge of node Fp will be more then Fn. Therefore transistor  $M_2$  and  $M_{I2}$ - $M_{I4}$  will be turned on before transistor  $M_1$  and  $M_9$ - $M_{II}$ . The output now start to charge and because of different discharging rate of node Fn and Fp, Outp charges at faster rate then Outn and reaches a voltage at which transistor  $M_6$  will be turned on and *Outn* will discharge to ground and *Outp* will be charge to  $V_{DD}$ . The circuits works Vice versa if Vinn>Vinp. In figure 3.6 the waveform of the proposed dynamic comparator is shown.

## III. FIGURES

Figure 3.1 Circuit diagram of conventional dynamic comparator

Figure 3.2 Transient simulation of conventional dynamic comparator for  $V_{CM} = 350 \text{mV}$ ,  $\Delta V_{in} = 100 \mu \text{V}$ ,  $V_{DD} = 0.4 \text{V}$

Figure 3.3 Circuit diagram of Double-tail Dynamic comparator

**Figure 3.4** Transient Simulation of Double tail Comparator for  $V_{CM} = 350 \text{mV}$ ,  $\Delta V_{in} = 100 \mu \text{V}$ ,  $V_{DD} = 0.4 \text{V}$ .

Figure 3.5 Circuit diagram of Proposed Dynamic comparator

Figure 3.6 Transient Simulation of Proposed dynamic Comparator for  $V_{CM} = 350 \text{mV}$ ,  $\Delta V_{in} = 100 \mu \text{V}$ ,  $V_{DD} = 0.4 \text{V}$ .

## IV. TABLES

Table 1. The performance comparison between conventional dynamic Comparator and double-tail dynamic comparator with differential input voltage of 100μV and common mode voltage of 350mV at 0.4V of power supply.

| Comparator<br>Structure | Conv <mark>entional Dynamic Comparator </mark> | Double-tail<br>Dynamic<br>Comparator |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| CMOS Technology         | 180 nm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 180 nm                               |

| Supply Voltage          | 0.4 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0.4 V                                |

| Sampling                | 400 KHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1 MHz                                |

| Frequency               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                      |

| Delay                   | 1.109 μs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 312.18 µs                            |

| Total Power             | 134.3 nW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 67.07 nW                             |

| Consumption             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                      |

Table 2. The performance comparison between double-tail dynamic comparator, proposed dynamic comparator operated in saturation region and proposed dynamic comparator operated in sub-threshold region with differential input voltage of 100μV and common mode voltage of 350mV.

| Comparator<br>Structure    | Double-tail Dynamic<br>Comparator [16] | Proposed<br>Dynamic<br>Comparator | Proposed Dynamic Comparator (Sub-threshold) |

|----------------------------|----------------------------------------|-----------------------------------|---------------------------------------------|

| CMOS Technology            | 180 nm                                 | 180 nm                            | 180 nm                                      |

| Supply Voltage             | 1.2 V                                  | 1.2 V                             | 0.4 V                                       |

| Sampling Frequency         | 500 MHz                                | 500 MHz                           | 2 MHz                                       |

| Delay                      | 550 ps                                 | 381.4 ps                          | 136.2 ns                                    |

| Total Power<br>Consumption | 329 μW                                 | 155.70 μW                         | 74.09 nW                                    |

**Remark.** A low power low delay time dynamic comparator has been presented which works both on sub-threshold and normal saturation region. The comparator consumes 74.09 nW power at a frequency of 2MHz and 136.2ns delay while working with 0.4 V supply voltage. When the supply voltage is 0.4 V, all the transistors are compelled to work in sub-threshold region. While working with 1.2 V supply voltage, it consumes 155.70  $\mu$ W power at a frequency of 500 MHz and delay as low as 381 ps. This comparator can detect a minimum input voltage difference of 100  $\mu$ V which is essential for EEG and ECG application.

As the proposed ultra-low power Dynamic Comparator consumes very low power with small delay time, it is suitable for the implantable biomedical devices such as cardiac and non-cardiac pacemaker.

### REFERENCES

- [1] Zhangming Zhu Guangwen Yu, Hongbing Wu, Yifei Zhang, Yintang Yang, "A high speed latched comparator with low offset voltage and low dissipation," Analog Integrated Circuits and Signal Processing, vol 74, Issue 2, pp. 467-471, Feb. 2013.

- [2] Ye, X. Ytterdal, "A loe offset dynamic comparator using bulk biasing technique in digital 65 nm CMOS technology," ICSICT, 10th IEEE International Conference, Shanghai, China, Nov. 1-4, Nov. 2010.

- [3] N. Stefanou, S.R Sonkusale, "An average low offset comparator for 1.25 Gsamples/s ADC in 180nm CMOS." ICECS, Proceedings of the 11th IEEE International Conference, Tel Aviv, Israel, pp. 13-15, Dec. 2004.

- [4] K. D. S., "A new offset cancelled latch comparator foe high speed, low offset ADCs." APCCAS, IEEE Asia Pacific Conference, Kuala Lumpur, Malaysia, Dec 6-9. Dec. 2010.

- [5] B. Goll and H. Zimmermann, "A 0.12μm CMOS comparator requiring 0.5V at 600MHz and 1.5V at 6GHz." In Proc. IEEE Int. Solid state Circuits Conf., Dig. Tech. Papers, pp.316-317, Feb. 2007.

- [6] B. Goll and H. Zimmermann, "A 65nm CMOS comparator with modified latch to achieve 7GHz/1.3mW at 1.2V and 700MHz/47μW at 0.6V," in Proc. IEEE Int. Solid State circuits Conf., Dig. Tech. Paper, pp. 328-329, Feb. 2009.

- [7] B. Goll and H. Zimmermann, "Low power 600MHz comparator for 0.5V supply voltage in 120nm CMOS," IEEE Electronics Letter, vol. 43, no. 7, pp. 388-390, Mar. 2007.

- [8] B. Goll and H. Zimmermann, "A comparator with reduced delay time in 65nm CMOS supply Voltage down to 0.65," IEEE Trans. Circuits Syst. II, Exp. Briefs, Nov. 2009. vol. 56, no. 11, pp. 810-814, Nov. 2009.

- [9] D. Shinkel, E. Mensink, E. Klumperink, E. Van Tuijl and B. Nauta, "A double tail latch type voltage sense amplifier with 18ps Setup+Hold time," in Proc. IEEE Int. Solid State Circuits Conf., Dig. Tech. Paper, pp. 314-315, Feb. 2007.

- [10] A. Nikoozadeh and B. Murmann, "An analysis of latched comparator offset due to load capacitor mismatch," IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 73, no. 3, pp. 1398-1402, Dec. 2006.

- [11] S. Babayan Mashhadi and R. Lofti, "An offset cancellation technique for comparator using body-voltage trimming," Int. J. Analog Integr. Circuits Signal Process, vol. 73, no. 3, pp. 673-682, Dec. 2012.

- [12] J. He, S. Zhan, D. Chen and R. J. Geiger, "Analysis of static and dynamic random offset voltage in dynamic comparator," IEEE Trans. Circuits Syst. I, Reg. Paper, vol. 56, no.5, pp. 911-919, May. 2009.

- [13] P. Nuzzo, F. D. Bernardinis, P. Terreni and G. Vander Plas, "Noise analysis of regeneration comparators foe reconfigurable ADC architectures," IEEE Trans. Circuits Sysr. I, Reg. Paper, vol. 55, no. 6, pp. 1441-1454, Jul. 2008.

- [14] P. M. Figueiredo and J. C. Vital, "Kickback noise reduction technique for CMOS latched comparatoes," IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 53, no. 2, pp. 541-545, Jul. 2006.

- [15] J. Kim, B. S. Leibowits, J. Ren and C. J. Madden, "Simulation and analysis of random decision errors in clocked comparators," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 56, no. 8, pp. 144-1857, Aug. 2009.

- [16] S. Babayan Mashhadi and R. Lofti, "Analysis and design of a low-voltage low-power double tail comparator," IEEE Trans. On VLSI systems, vol. 22, no. 2, pp. 343-352, Feb. 2014.